<del id="aymay"></del> 跳頻技術是一種具有高抗干擾性、高抗截獲能力的擴頻技術[1]。接收系統是跳頻通信系統中非常重要的部分,自適應跳頻技術、高速跳頻技術、信道編碼技術、高效調制解調技術成為近年來跳頻技術發展的新動態,基于FPGA的跳頻通信接收系統[2]研究有很高的應用價值。

跳頻電臺就是采用了頻率跳變來擴展頻譜,提高抗干擾能力,在軍事通信中得到了廣泛的應用[3]。基于FPGA+DSP的跳頻電臺傳輸系統的設計方案[4]具有很好的可移植性。無線通信調制解調紛繁復雜,數碼率及誤碼率要求也不盡相同,該傳輸系統還需要能夠自適應地檢測跳頻電臺的時鐘信息及同步碼,并進行相應的處理,以滿足業務速率的接收解調。

本文系統中采用Xilinx公司的VIRTEX5 XC5VSX50T668 FPGA,該芯片具有先進的高性能邏輯架構,包含多種硬IP系統級模塊,并且還支持以太網與PCI Exprees端點模塊。其中RocketIO GTP收發器的設計運行速度為100 Mb/s~3.75 Gb/s,RocketIO GTX收發器的設計運行速度為150 Mb/s~6.5 Gb/s。

1 系統總體架構

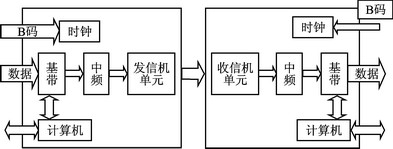

該系統采取半雙工形式進行工作,通過 PTT進行收/發切換。高速跳頻通信系統可具體化為發送狀態模型和接收狀態模型。本系統的硬件設備分為兩個實體,一個負責發送數據,一個負責接收數據,主要的軟件工作在基帶板和中頻板卡上。系統總體框架圖如圖1所示。

圖1 系統總體框架圖

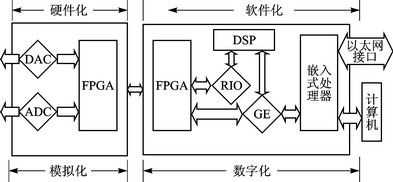

基帶板芯片主要包括FPGA和DSP,處理器間使用RapidIO接口交換數據,中頻板主要由FPGA和AD/DA轉換芯片組成,基帶板和中頻板通過高速SERDES傳輸信號數據,基帶信號經過信道編碼、交織、軟擴頻,然后添加同步頭,組成特定的幀格式后,寫入FPGA 的發送消息存儲區,其結構圖如圖2所示。

圖2 基帶板與中頻板框圖

從圖2可以看出,在發送端,數據終端或語音終端將數字信息送入基帶信號處理器(高速通用FPGA+DSP),然后DSP 對這些數字信息進行基帶處理,得到數字化的基帶信號并送入FPGA 進行數字中頻處理(頻譜上搬移過程),用數字化的方法將信號搬移中頻上,數字化的中頻信號再經過寬帶D/A轉換器轉化為模擬信號,最后經由射頻電路將載有信息的電磁波送入自由空間。