<del id="aymay"></del> 一部分工程師會使用Verilog來設計邏輯電路圖,作為目前世界上最流行的兩種硬件描述語言,Verilog不僅能夠對電路圖進行表示,還能夠進行一些計算。本篇文章就將為大家介紹Verilog當中任意占空比和分頻的的實現方法。

在verilog程序設計中,我們往往要對一個頻率進行任意分頻,而且占空比也有一定的要求。這樣的話,對于程序就會有一定的要求,本篇文章將在前人經驗的基礎上做一個簡單的總結,實現對一個頻率的任意占空比以及任意分頻的確定。

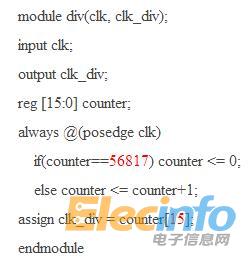

比如:我們FPGA系統時鐘是50M Hz,而我們要產生的頻率是880Hz,那么,我們需要對系統時鐘進行分頻。我們很容易想到用計數的方式來分頻:

50000000/880 = 56818

這個數字不是2的整冪次方,那么怎么辦呢?我們可以設定一個參數,讓它到56818的時候重新計數不就完了嗎?程序如下:

在我們日常的設計中很多情形下會用到需要分頻的情形,好多人的做法是先用高頻時鐘計數,然后使用計數器的某一位輸出作為工作時鐘,進行其他的邏輯設計,上面的程序就是一個體現。

下面我們來算一下它的占空比:我們清楚地知道,這個輸出波形在counter為0到32767的時候表現為低,在32768到56817的時候為高,占空比為40%多一些,如果我們需要占空比為50%,那么怎么辦呢?

我們再設定一個參數,使它為56817的一半,使達到它的時候波形翻轉:

占空比是不是神奇地變成50%了呢?

繼續讓我們來看如何實現任意占空比,比如還是由50 M 分頻產生880 Hz,而分頻得到的信號的占空比為30%。