<del id="aymay"></del> 網上有很多關于fpga的總結和分析,但都是基于軟件調試的角度來進行分析的,本文則選擇了FPGA硬件的電路板來進行相關的分析,并且著重FPGA電路板的可測試性設計。所謂可測試性,很簡單,就是在板級調試的時候,更方便調試,判決準則就是想看什么信號就可以看到什么信號。

電源電路設計

在進行電源電路的設計時,我們可以在電路的輸出處增加一些跳線,在電源電路沒有調通之前,可以確保電源不會輸出到下一部分電路,保證后續電路的安全,而電源電路部分,應該加上足夠的測試點,包括反饋電壓點、輸出電源點以及地測試點,建議在PCB設計的時候,在電源輸出測試點處就近放一個地測試點,個人不建議測量電壓的時候,萬用表的表筆直接點在電容或者電感上。

建議用LED指示燈來標記電源的輸出處,這樣的話板子是否進行正常的工作就一目了然了。

FPGA信號測試

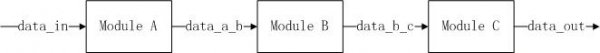

曾經做過FPGA半調試的朋友肯定都有這樣的感覺,當板子的調試出現問題時,非常想把板子拆開,然后把邏輯分析儀或者數字示波器接入到內部信號通道的每個模塊的輸入輸出端口處,看下波形,分析問題到底出在什么地方。雖然有chipscope/signaltap這樣的輔助分析工具,但FPGA內部資源畢竟有限,不可能做到隨意查看信號。

所以我們可以從FPGA上入手,如果在設計上還有未使用的引腳,我們可以引出8根或者16根線來,作為專用調試管腳,在PCB設計時連到一個排插上,用于調試,觀察內部節點信號的波形,以下圖為例,進行描述: