<del id="aymay"></del> 在工業生產自動化系統中,通過計算機視覺和圖像處理技術來實現產品的質量監測和控制,已逐漸成為一種有效的應用技術。線陣CCD 圖像傳感器廣泛地應用于產品尺寸測量和分類、非接觸尺寸測量、條形碼、形態識別等眾多領域。在圖像檢測系統中,應具備一個高速的子圖像提取和輸出模塊,本文采用FPGA 器件EP3C25F256C8 和CCD 線陣圖像傳感器RL1024P,實現線陣CCD 圖像檢測系統中的子圖像提取和輸出功能。

1 子圖像提取模塊的設計

子圖像提取模塊的功能可描述為:采用FPGA 器件實現,根據串行輸入的黑白圖像和同步信號,提取該圖像中設定尺寸大小的子圖像。假設輸入圖像大小為i * j,某一像素點的坐標位置為(X,Y),要取出子圖像的大小為m * n,則用c 代碼描述為:for(b=0;b《j ; b++){for (a=0;a《i; a++){ // 取出Xa,Yb 到 Xa+m,Yb+n 的子圖像;} }

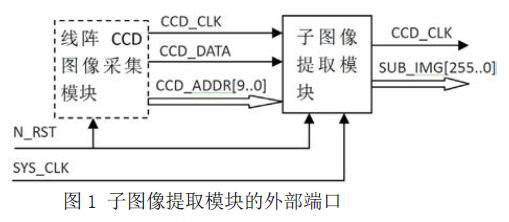

根據系統設計的要求,線陣CCD 圖像采集模塊采用串行的方式輸出1×1024 像素的一行圖像,子圖像提取模塊接收該圖像數據、緩沖、再輸出16×16 像素的子圖像。子圖像提取模塊的外部端口,如圖1 所示。主要信號有:像素同步時鐘信號CCD_CLK、像素數據CCD_DATA、當前輸入像素的坐標CCD_ADDR[90] ;另外,N_RST 和SYS_CLK 為系統提供的復位信號和處理時鐘信號。其中,每個CCD_CLK 的上升沿出現時CCD_DATA 像素有效,且該像素所在的位置為CCD_ADDR[90] 值。

為了實現每個CCD_CLK 周期內均輸出一個子圖像,SYS_CLK應該為CCD_CLK 的10 倍左右。

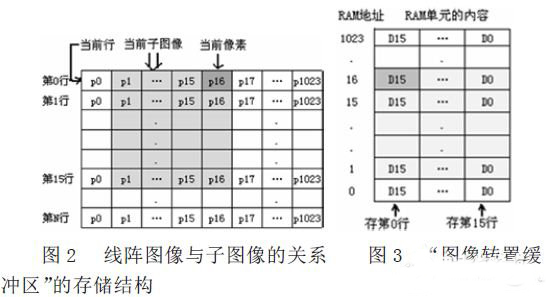

本文采用“圖像轉置緩沖區”的方法來實現子圖像提取模塊。“圖像轉置緩沖區”是一個按行寫入(更新)、按列讀出的一個RAM 緩沖區。在FPGA 內部設置一個1024 個單元的RAM 緩沖區,每個單元的位寬為16bits.線陣CCD 采集模塊輸出的線陣圖像與子圖像的關系,如圖2 所示。其中,第0 行表示圖像的當前行,第N 行為歷史行,每行有1024 個像素,按照p0 至p1023 的像素順序輸出。假設當前CCD_CLK 輸入的像素為第0行的p16 像素,則其對應的16X16 子圖像為圖中的陰影部分。

“圖像轉置緩沖區”RAM 塊存儲圖像的結構,如圖3 所示。

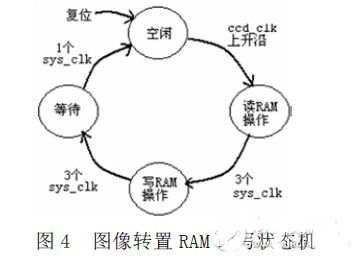

RAM 塊共有1024 個單元,每個單元為16 位的寬度,可存放最近的16 行圖像數據。對比圖2 和圖3,可以發現,RAM 塊的地址編號相當于線陣CCD 圖像的某一行像素的位置,某個RAM單元的位D15 ~ D0 對應某一列的最近16 個像素,相當于對線陣圖像轉置后再存放到RAM 塊中。對RAM 緩沖區進行寫操作時,由于線陣CCD 圖像的數據是按行逐位輸入的,每個CCD_CLK 時鐘上升沿出現時,僅需更新RAM 緩沖區中當前像素對應的比特,因此在邏輯上是根據圖像按行寫入RAM 區的。在FPGA器件中,可設計一個狀態機來實現“圖像轉置緩沖區”的讀寫操作,如圖4 所示。

子圖像提取模塊輸出的子圖像有256 個像素,在FPGA 內部通過寄存器暫存上一個輸出的子圖像;當更新RAM 區的某個像素時,把16X16 的滑動窗口向右移動一列像素的位置,把滑動窗口內的數據作為輸出,就可以得到新的子圖像。

2 設計仿真

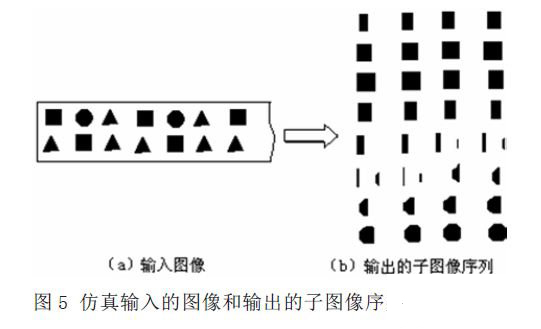

在本文的設計仿真中,由于用到圖像文件的解析和圖像顯示,因此借助MATLAB 和Modelsim 軟件,通過文件讀寫的方式實現的聯合仿真,可使仿真處理更加便捷和直觀。其中,MATLAB 用來把圖像文件轉換為輸入的像素,以及顯示輸出的子圖像;Modelsim 用來仿真和驗證FPGA 設計是否正確。

本文使用MATLAB 和Modelsim 進行聯合仿真,主要有以下三個步驟。第一步,在MATLAB 中編寫m 文件,讀取bmp 位圖文件并把像素數據寫入文件datain.txt 中,作為ModelSim仿真的輸入激勵信號。第二步,在ModelSim 中,用VHDL 編寫Testbench 測試文件,讀取datain.txt 文件,產生與CCD_CLK 同步的像素信號;編寫DO 文件進行自動化仿真,再把仿真輸出的子圖像數據保存在dataout.txt 文件中。第三步,在MATLAB 中編寫m 文件,解析dataout.txt 文件,依次顯示為16×16 的黑白圖片序列,確定仿真結果是否正確。本設計仿真輸入的圖像及輸出的子圖像序列,如圖5 所示。從仿真結果可知,設計方法是正確的,仿真結果符合設計功能的要求。

3 結束語

應用線陣CCD 圖像傳感器進行產品檢測時,連續、高速地輸出子圖像序列是必不可少的重要環節,采用FPGA 實現子圖像序列的提取和輸出,有多種不同的設計方法。本文采用“圖像轉置緩沖區”和狀態機的方式,來實現系統所要求的子圖像提取和輸出的功能,并用MATLAB 和ModelSim 工具軟件對設計進行了聯合仿真,該方法具有FPGA 資源占用少、結構簡單、高速處理,以及便捷和直觀的特點,對其他類似的FPGA 設計項目有很好的參考作用。