<del id="aymay"></del> 以FPGA作為核心處理器,提出基于FPGA多路機載冗余圖像處理系統的設計,本方案實現了對多路DVI視頻冗余信號的解碼、編碼、實時處理以及輸出顯示,并且信號通道增加冗余設計,因而加強了系統的穩定性和可靠性。方案中的電路設計簡潔,具有較強的靈活性和擴展性。通過實際測試結果表明,系統能夠流暢地對1 600×1 200分辨率,60 Hz刷新率,24位真彩色的高清視頻進行實時處理,其系統可靠、穩定,實用性強。

DVI(數字視頻接口)是當前數字顯示領域研究和應用的熱點,面向DVI輸出的視頻處理技術不僅解決了顯示器高分辨率、高刷新率等問題,而且提高了穩定性和顯示性能,并進一步降低了平板顯示器的成本。因此,面向DVI輸出的視頻控制器的研究具有十分重要的現實意義。

根據DVI標準,一條TMDS通道可以達到165 MHz的工作頻率和10 b 接口,也就是可以提供1.65 Gb/s的帶寬,這足以應付1 920×1 080@60 Hz(23寸LCD)的顯示要求。另外,為了擴充兼容性,DVI還可以使用第二條TMDS通道,這樣其帶寬將會超過3 Gb/s.也正是由于其較高的帶寬優勢,目前DVI已經成為了IT業界最具前途的規范。

DVI具有支持高帶寬數據傳輸和高清晰圖像顯示的優點。模擬視頻的顯示是通過數字到模擬到數字的轉化實現的,而DVI接口無需進行這些轉換,直接數字到數字,避免了信號轉換而帶來的圖像質量損失,使圖像的清晰度和細節表現力都得到了大大提高。基于以上優點,DVI接口被廣泛應用于航空、航天等領域。

1 總體方案設計

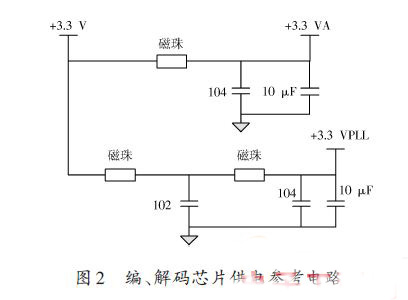

1.1 總體方案原理框圖

用戶輸入4路DVI信號,然后根據輸入信號特性進行選擇,將視頻信號實時顯示在液晶屏上。另外,將實時顯示的圖像回送給記錄儀,此時記錄儀實時記錄當前的信息以及故障信息,確保在全任務階段圖像顯示的正確性。根據設計要求,選擇Altera公司生產的FPGA 芯片EP2S30F1020I4 為主控芯片,配置芯片選用EPCS16SI16N.利用FPGA內部豐富的邏輯資源和強大的IP核,配以相應的外部電路,構建出一個靈活、簡潔、可靠的機載視頻圖形處理系統的嵌入式硬件模塊。其總體方案原理框圖如圖1所示。

1.2 DVI編解碼設計

在很多設計中,設計人員為了方便,簡化電路,可能不會增加均衡器,對輸入信號不進行處理。從而在后期的產品試驗過程中,很容易就會出現信號顯示質量差,兼容性差的缺陷,導致整個產品重新設計或整改,延緩了產品交貨進度。根據用戶輸入的視頻特性,本文采用均衡器+DVI編、解碼器的方式,對輸入、輸出信號進行轉換處理。這樣處理有如下優點:傳輸距離較長,信號干擾小;外圍電路簡單,設計靈活、可靠;系統速度快、靈活性強、功能可擴展,系統兼容性好。

在本系統中,選用TI 公司生產的均衡器DS16EV5110,該器件具有功耗低、體積小、外圍電路簡單等特點。另外,DVI編解碼芯片選用TI公司生產的芯片TFP401和TFP410,同樣具有功耗低、體積小、外圍電路簡單等特點。該器件控制引腳直接連接至FPGA,可以很好控制這些器件的工作狀態,以便減小功耗。并且,整個FPGA內部邏輯控制簡單、可靠。

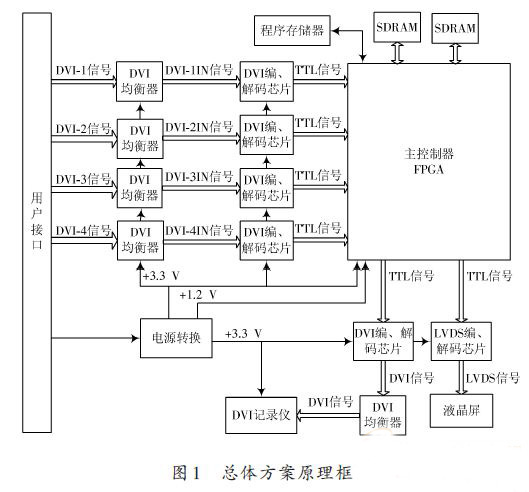

在硬件電路設計中,還需要考慮高頻特性對信號的影響。整個系統顯示的分辨率為1 600×1 200@60 Hz,信號位為真彩色24 b,采用奇偶方式,參考時鐘162 MHz,DVI編碼時鐘為10×162 MHz=1.62 GHz,其編碼碼元理論寬度僅為t = 1 1.62 Hz=0.62 ns,則碼元的最大變化時間應在0.62 4 = 0.16 ns之內。考慮數據傳輸的可靠性和穩定性,采用雙像素傳輸,可以大大降低信號采樣頻率。此外,還要考慮到PCB布局地線的完整性和供電去耦特性。其編解碼芯片混合信號的供電參考電路如圖2所示。